On December 22, Shanghai Minisilicon Technology Co., Ltd. (hereinafter referred to as " Minisilicon ") announced the successful tape-out and core functional verification of the world's first 4x112G ASP (Analog Signal Processor, containing CDR module) TxRx Chipsets. This innovative analog solution completely breaks the absolute monopoly of oDSP solutions in the high-speed optical module field, providing a new supply chain path for AIGC by less latency, less power consumption, and lower cost. It marks China's official transition from a "follower" to a "leader" in the high-speed opto-electronic chip domain. This series of ASP (CDR) electronic chips from Minisilicon has already secured deep collaboration with leading optical module company, jointly winning a National Key R&D Program of China's Ministry of Science and Technology.

Luo Gang, Founder of Minisilicon stated: "Since its founding in 2020, Minisilicon has focused on one thing: tackling technology head-on, because we believe the greatest innovation is not following, but blazing a new trail."

Industry Background: In the 400G-3.2T Era, Electronic Chips Are the 'Chokepoint' of AI Computing Infrastructure

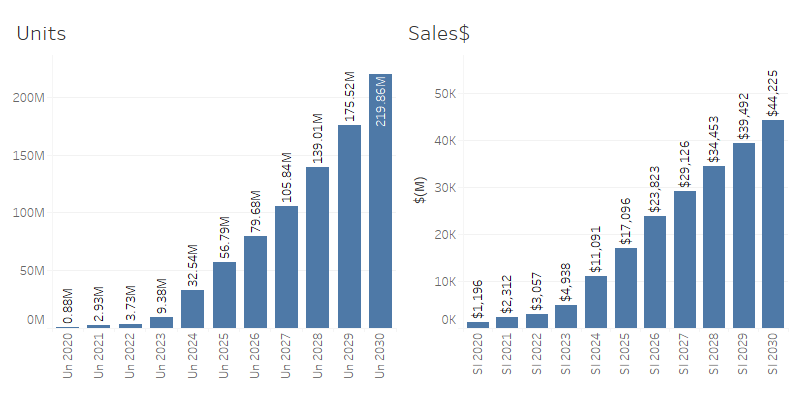

According to LightCounting's August 2025 report and predictions from listed companies' prospectuses, global shipments of 400G and above optical modules will exceed 100 million units by 2027, corresponding to a nearly $6 billion market for electronic chips (including oDSP, CDR, TIA, Driver). By 2030, the electronic chip market is projected to surpass $10 billion. While oDSP chips exhibit rapid growth and high technical barriers, ASP (CDR) electronic chips, as an alternative solution, hold vast market potential.

Data sourced from LightCounting Data Market Forecast, August 2025 edition

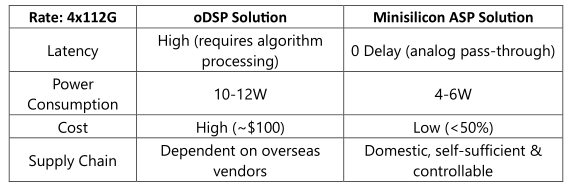

Over the past five years, the high-speed optical module electronic chip market for 400G and above has been almost entirely dominated by overseas oDSP vendors (e.g., Broadcom, Marvell). Their core technology involves using ADCs to digitize analog signals and employing mathematical algorithms to compensate for fiber loss, dispersion, and nonlinear effects—analogous to using Photoshop's AI algorithms for pixel-by-pixel restoration, capable of handling complex signals like PAM4/coherent modulation. Although powerful, oDSP presents three major pain points:

● High Cost: A single oDSP chip can cost tens to over a hundred dollars.

● High Power Consumption: Typical power consumption ranges from 10-12W, constraining computing power center PUE (Power Usage Effectiveness).

● Supply Chain Risk: Heavy reliance on overseas vendors poses a constant risk of disruption under geopolitical tensions.

This directly leads to constraints not only on compute GPU supply but also on core electronic chips for high-speed optical modules within China's AI computing infrastructure.

Market Landscape: From 'Following' to 'Leading,' the 'Overtaking' Moment for Domestic Electronic Chips

Currently, domestic electronic chip manufacturers are mostly concentrated in the 100G and below market, leaving the 400G+ high-end market nearly blank. Minisilicon has chosen a "more pragmatic" path—the ASP (CDR) electronic chip solution.

Its technical principle involves directly stabilizing signals through analog circuits (phase detector, phase-locked loop PLL, frequency detector), eliminating the need for complex digital algorithm compensation. This delivers three significant advantages:

● Cost Reduction of 50%-70%: Fully self-developed, requiring no expensive DSP cores or AI algorithm licensing.

● Power Reduction of 50%: Typical power consumption of 4~6W, significantly alleviating cooling pressure in computing centers.

● Breaking Technological Dependence: Achieving fundamental self-sufficiency and control.

Technical Barrier: Why is ASP (CDR) the Future Moat?

Many consider "analog circuits as old technology," but the difficulty of high-speed analog electronic chips far exceeds imagination. For ASP (CDR: Clock and Data Recovery) at 112Gbps rates, achieving the following is required:

● Picosecond-level clock jitter control

● Ultra-low noise amplification and filtering

● Complex channel equalization and eye diagram optimization

All these require profound analog circuit design expertise—utilizing phase-locked loops (PLL), phase detectors, and ultra-low-noise amplifiers to directly align and recover data—coupled with process optimization capabilities and a deep understanding of high-speed signal integrity. The fact that Minisilicon has been able to achieve this breakthrough ahead of others is precisely due to its "decade of dedicated refinement" in technological accumulation. More importantly, the ASP (CDR) solution inherently possesses "moat" attributes:

● High Technical Barrier: Analog circuit design relies on accumulated experience, making it difficult to replicate quickly.

● Deep Ecosystem Integration: Deep collaboration with optical module manufacturers forms a combined "chip + module" advantage.

Strategic Significance: Breaking the Mold with Innovation, from Follower to Leader

Driven by the global wave of AI compute infrastructure competition, high-speed optical module electronic chips have evolved from "electronic components" to critical pivots of "computing infrastructure." The long-term monopoly by overseas giants on 400G/800G optical module oDSP chips has posed severe challenges to domestic supply chain security.

Minisilicon Tech's world-first 4x112G ASP (CDR) electronic chip pioneers a new alternative path—directly replacing the complex oDSP+Driver+TIA solution, providing optical module manufacturers with a higher integration, lower cost, and superior power efficiency solution. Its strategic significance lies in:

● Breaking the overseas oDSP monopoly, achieving "domestic substitution."

● Reducing Data Center TCO (Total Cost of Ownership), supporting "Dual Carbon" goals.

● Building a self-sufficient and controllable high-speed computing chip supply chain.

● Laying the foundation for subsequent 1.6T, 3.2T high-speed interconnect electronic chip R&D.